集成電路(IC)設計是將復雜的電子電路功能集成到一小塊半導體芯片上的過程。其基本流程主要包括以下幾個階段:

一、需求分析與規格制定

在設計開始前,首先必須明確系統的功能需求、性能指標、功耗要求、成本預算及封裝形式等。這一階段需要與客戶或系統工程師密切溝通,形成詳細的設計規格文檔,作為后續設計的依據。

二、架構設計

根據規格要求,設計團隊將系統劃分為多個功能模塊,并確定各模塊之間的接口和數據流向。此階段可能涉及選擇處理器核心、內存架構、總線結構等關鍵組件,并進行初步的性能和功耗評估。

三、邏輯設計

在架構確定后,工程師使用硬件描述語言(如Verilog或VHDL)編寫每個功能模塊的寄存器傳輸級(RTL)代碼。RTL描述定義了數字電路在時鐘沿觸發時的數據流動和存儲行為。隨后,通過功能仿真驗證代碼的正確性。

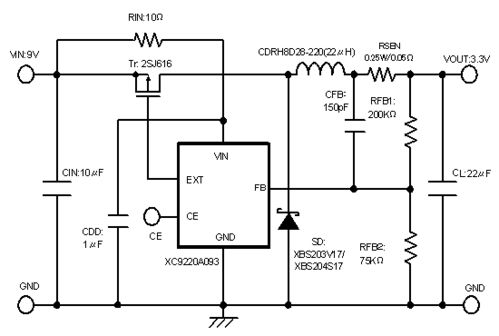

四、邏輯綜合

將RTL代碼轉換為門級網表的過程稱為邏輯綜合。設計者設定時序、面積和功耗等約束條件,綜合工具根據標準單元庫生成由基本邏輯門(如與門、或門、觸發器等)組成的電路結構。綜合后需進行靜態時序分析,確保電路滿足時序要求。

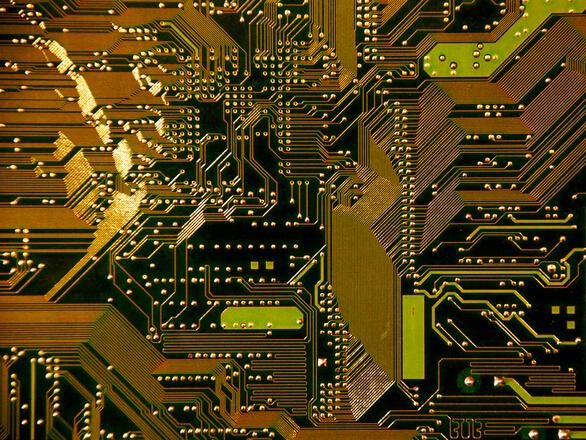

五、物理設計

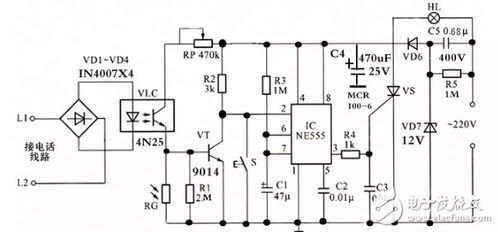

物理設計是將邏輯網表映射到實際芯片布局的過程,包括以下步驟:

- 布局規劃:確定芯片上各個模塊的位置和形狀,規劃電源網絡和時鐘樹。

- 布局:將標準單元和宏模塊放置在芯片的適當位置。

- 布線:根據電路連接關系,在單元之間鋪設金屬連線。

- 物理驗證:檢查設計規則(DRC)、電氣規則(ERC)和版圖與原理圖一致性(LVS),確保制造可行性。

六、后仿真與簽核

完成物理設計后,提取版圖的寄生參數(電阻、電容),進行帶有時序信息的后仿真,以驗證電路在實際布局下的性能。同時,進行最終的時序、功耗和信號完整性分析,達到簽核標準后方可交付制造。

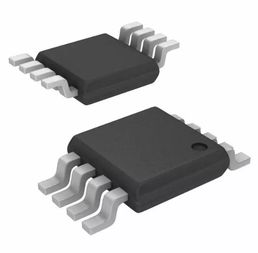

七、制造與測試

將設計數據(通常為GDSII格式)發送至半導體代工廠進行光罩制作和晶圓制造。芯片制造完成后,需進行嚴格的測試,包括晶圓測試和封裝后測試,以確保功能正確和可靠性達標。

集成電路設計是一個迭代和高度協作的過程,涉及EDA工具鏈的廣泛應用和跨學科知識的整合。隨著工藝節點不斷縮小,設計復雜度日益增加,對設計方法學和團隊協作提出了更高要求。