ERPOM(Electrically Erasable Programmable Read-Only Memory,電可擦可編程只讀存儲器)是一種非易失性存儲器,廣泛應用于集成電路設計中。它允許通過電信號進行數據的寫入、擦除和讀取,具有高可靠性、低功耗和可重復編程的特點。以下將詳細介紹ERPOM的基本結構和工作原理,并探討其在集成電路設計中的應用。

一、ERPOM的基本結構

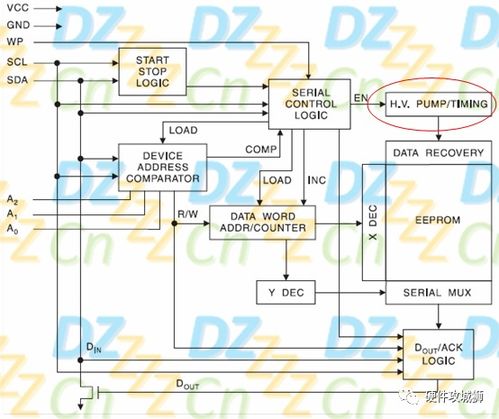

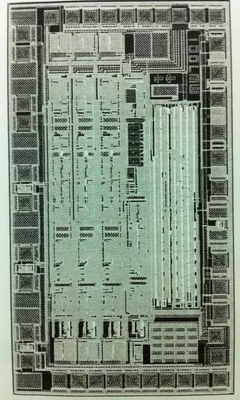

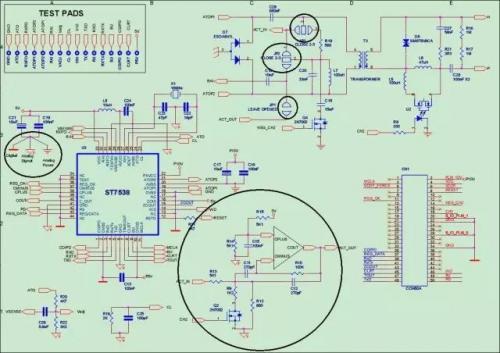

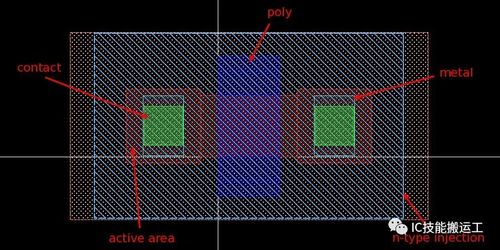

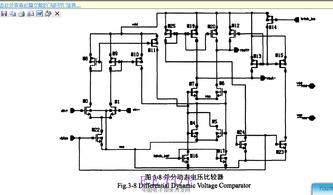

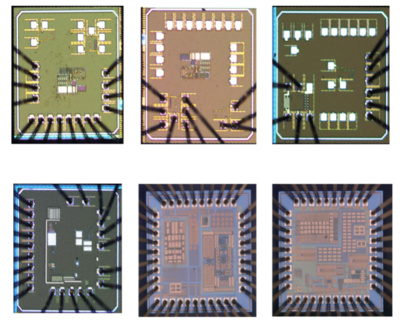

ERPOM的基本結構主要由存儲單元陣列、地址譯碼器、讀寫控制電路和輸出緩沖器組成。存儲單元是核心部分,每個單元包含一個浮柵晶體管,用于存儲電荷表示數據(通常,電荷存在表示邏輯'0',無電荷表示邏輯'1')。浮柵被絕緣層包圍,電荷可以長時間保留,實現非易失性存儲。地址譯碼器負責將輸入的地址信號轉換為具體的存儲單元選擇信號,讀寫控制電路管理數據的寫入、擦除和讀取操作,而輸出緩沖器則放大讀取的數據信號以確保穩定性。

二、ERPOM的工作原理

ERPOM的工作原理基于浮柵晶體管的電荷存儲機制。在寫入數據時,通過施加較高的電壓(通常為12-20V),電子通過隧道效應注入浮柵,改變晶體管的閾值電壓,從而存儲數據。擦除操作則通過施加反向電壓或紫外線(在某些早期版本中)移除浮柵中的電荷,恢復初始狀態。讀取數據時,施加較低的電壓檢測晶體管的導通狀態:如果浮柵有電荷,晶體管不導通,輸出邏輯'0';反之輸出邏輯'1'。整個過程由控制電路精確管理,確保數據的正確性和耐久性。ERPOM的擦寫次數通常可達10萬次以上,適用于頻繁更新的應用場景。

三、ERPOM在集成電路設計中的應用

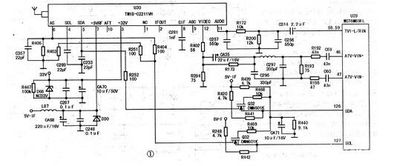

在集成電路設計中,ERPOM常用于存儲固件、配置數據或校準參數,例如在微控制器、智能卡和嵌入式系統中。它的可編程性和非易失性使得系統可以在斷電后保留數據,同時支持在線更新,提高了設計的靈活性。設計時需考慮功耗、面積和速度的平衡,采用CMOS工藝集成ERPOM單元以降低功耗。ERPOM的可靠性測試(如數據保持時間和耐久性)是集成電路驗證的關鍵環節,確保其在各種環境下的穩定運行。

ERPOM作為一種重要的存儲器技術,其結構簡單、工作原理可靠,在集成電路設計中發揮著關鍵作用。隨著技術的發展,ERPOM已演變為更先進的EEPROM和Flash存儲器,但其基本原理仍是現代存儲設計的基礎。