在當(dāng)今高度集成的電子系統(tǒng)中,射頻集成電路(RFIC)與數(shù)字電路(Digital IC)不再是孤立發(fā)展的技術(shù)分支,而是緊密交織、相互依存的有機(jī)整體。它們的協(xié)同設(shè)計(jì)與深度融合,是推動(dòng)現(xiàn)代無(wú)線通信、物聯(lián)網(wǎng)、人工智能等前沿技術(shù)發(fā)展的核心引擎。本文將探討射頻集成電路與數(shù)字電路之間的聯(lián)系,并闡述它們?cè)诩呻娐吩O(shè)計(jì)層面的相互作用與未來(lái)趨勢(shì)。

一、 根本區(qū)別:模擬與數(shù)字的本質(zhì)分野

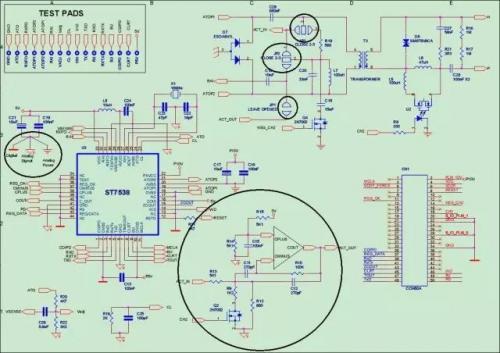

要理解二者的聯(lián)系,首先需明確其基本差異。射頻集成電路處理的是高頻(通常從數(shù)百M(fèi)Hz到數(shù)十GHz甚至更高)模擬信號(hào),其核心在于信號(hào)的放大、調(diào)制、解調(diào)、濾波和頻率變換,設(shè)計(jì)需重點(diǎn)關(guān)注噪聲、線性度、阻抗匹配、功耗和工藝變異等模擬特性。而數(shù)字電路處理的是離散的“0”和“1”信號(hào),核心在于邏輯運(yùn)算、數(shù)據(jù)存儲(chǔ)與處理,設(shè)計(jì)更關(guān)注時(shí)序、功耗、面積和可測(cè)試性。

二、 核心聯(lián)系:系統(tǒng)級(jí)協(xié)同與信號(hào)鏈閉環(huán)

盡管底層原理不同,但RFIC與數(shù)字電路在系統(tǒng)層面構(gòu)成了一個(gè)完整的信號(hào)處理閉環(huán),其聯(lián)系主要體現(xiàn)在以下幾個(gè)方面:

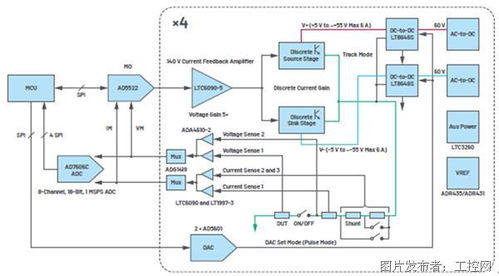

- 互補(bǔ)的功能角色:在一個(gè)典型的無(wú)線收發(fā)系統(tǒng)中,RFIC(如低噪聲放大器、混頻器、功率放大器、壓控振蕩器)負(fù)責(zé)“前端”工作,即在天線與數(shù)字基帶之間進(jìn)行模擬射頻信號(hào)的收發(fā)與轉(zhuǎn)換。而數(shù)字電路(如數(shù)字信號(hào)處理器、微控制器、基帶處理器)則負(fù)責(zé)“后端”工作,即對(duì)轉(zhuǎn)換后的數(shù)字信號(hào)進(jìn)行編解碼、加密、協(xié)議處理與應(yīng)用計(jì)算。二者缺一不可,共同完成從空中波形到可用數(shù)據(jù)的全過(guò)程。

- 接口與數(shù)據(jù)轉(zhuǎn)換:模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)是連接RFIC與數(shù)字電路的物理與邏輯橋梁。高性能的ADC/DAC使得數(shù)字電路能夠更深入地參與射頻信號(hào)的處理(如數(shù)字中頻、軟件定義無(wú)線電),而數(shù)字電路生成的數(shù)字控制字(如用于自動(dòng)增益控制、頻率校準(zhǔn))又能精確地調(diào)控RFIC的工作狀態(tài),實(shí)現(xiàn)自適應(yīng)與智能化。

- 設(shè)計(jì)方法的交叉與輔助:

- 數(shù)字輔助射頻:利用數(shù)字電路的精確性和可編程性,來(lái)校準(zhǔn)、補(bǔ)償或增強(qiáng)RFIC的性能。例如,使用數(shù)字算法進(jìn)行IQ失衡校正、數(shù)字預(yù)失真以改善功率放大器線性度、數(shù)字鎖相環(huán)替代部分模擬電路等。這能降低對(duì)模擬工藝精度的依賴,提高成品率和可靠性。

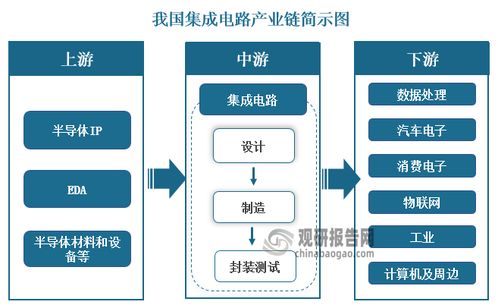

- EDA工具與流程的融合:先進(jìn)的集成電路設(shè)計(jì)需要統(tǒng)一的EDA平臺(tái),能夠同時(shí)處理射頻模擬和數(shù)字設(shè)計(jì)。雖然仿真工具側(cè)重點(diǎn)不同(如ADS用于射頻,Genus/Innovus用于數(shù)字),但系統(tǒng)級(jí)協(xié)同仿真、混合信號(hào)驗(yàn)證以及物理設(shè)計(jì)時(shí)的布局布線協(xié)同(考慮噪聲隔離、襯底耦合等)變得至關(guān)重要。

三、 集成電路設(shè)計(jì)中的挑戰(zhàn)與趨勢(shì)

- 工藝技術(shù)的統(tǒng)一:SoC與先進(jìn)制程:隨著CMOS工藝尺寸不斷縮小,在單一芯片上集成射頻前端、模擬接口和復(fù)雜數(shù)字邏輯的系統(tǒng)級(jí)芯片(SoC)成為主流。這使得RFIC設(shè)計(jì)必須適應(yīng)以數(shù)字為導(dǎo)向的先進(jìn)工藝(如FinFET),面臨柵極泄漏、低電源電壓、器件模型精度等新挑戰(zhàn),但同時(shí)也能受益于高集成度、低功耗和低成本的優(yōu)勢(shì)。

- 設(shè)計(jì)與驗(yàn)證的復(fù)雜性:混合信號(hào)SoC的設(shè)計(jì)驗(yàn)證是巨大挑戰(zhàn)。需要建立從系統(tǒng)行為級(jí)、晶體管級(jí)到版圖后仿真的完整驗(yàn)證流程,確保數(shù)字開(kāi)關(guān)噪聲對(duì)敏感射頻電路的干擾在可控范圍內(nèi)(通過(guò)良好的電源分布、隔離結(jié)構(gòu)和襯底接觸設(shè)計(jì))。

- 軟硬件協(xié)同與智能化:未來(lái)的聯(lián)系將更加緊密,走向“智能射頻”。數(shù)字電路中的處理器或?qū)S肁I加速器,可以實(shí)時(shí)分析射頻信號(hào)特征,動(dòng)態(tài)配置RFIC參數(shù),實(shí)現(xiàn)更高效的頻譜利用、抗干擾和節(jié)能,邁向認(rèn)知無(wú)線電與通信感知一體化。

結(jié)論

射頻集成電路與數(shù)字電路之間的聯(lián)系,已從簡(jiǎn)單的“前后級(jí)串聯(lián)”演變?yōu)樯疃鹊摹肮δ苋诤吓c智能協(xié)同”。在集成電路設(shè)計(jì)領(lǐng)域,設(shè)計(jì)師必須具備跨領(lǐng)域的知識(shí)體系,既要精通晶體管級(jí)的模擬藝術(shù),也要掌握系統(tǒng)級(jí)的數(shù)字架構(gòu)與算法。兩者的界限正在工藝進(jìn)步和設(shè)計(jì)創(chuàng)新的驅(qū)動(dòng)下變得模糊,其協(xié)同進(jìn)化將繼續(xù)定義下一代高性能、高集成度電子系統(tǒng)的形態(tài)與能力。